Reseach In Progress

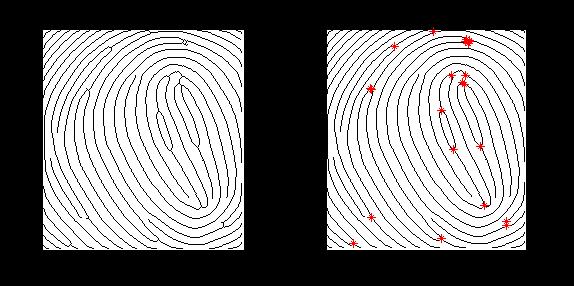

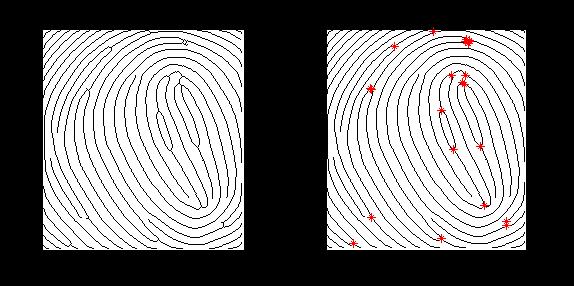

Fingerprint identification is one of the most important biometric technologies which have drawn a substantial amount of attention recently; many algorithms have been developed to allow a reliable automatic fingertip verification system. A key step in these algorithms is the accurate extraction

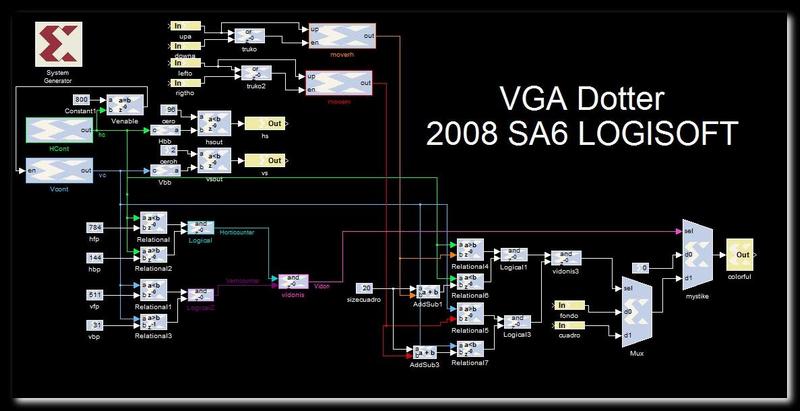

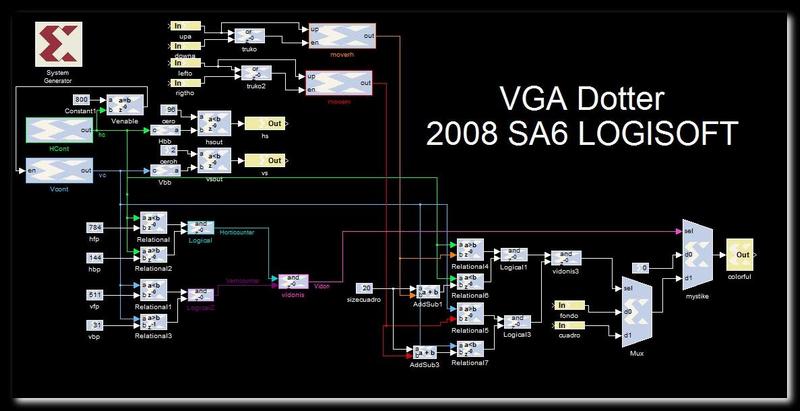

of the minutiae from the input image. However the performance of a minutiae extraction algorithm relies heavily on the quality of this input, hence, in order to ensure the accuracy of the identification system it is essential to include the system with an adequate a fingerprint enhancement algorithm. In this paper we discus the possibility of successfully implement a fingerprint recognition system in a FPGA, taking advantage of the inherent parallelism of this devices.

The algorithm that will be used as reference for the system base its effectiveness in the image enhancement to accurately locate the minutiae, and the neuronal network to make a reliable comparison between the actual fingerprint and the database. There is a description of the algorithm phases.

Image Acquisition: obtained via optic device with a resolution of 340x340 pixel in 8bit grayscale

Image enhancement: Due to the fact that the algorithm heavily relies in the quality of the image, it uses two filters, one using the FFT and the other the Gabor filtering.

Binarization: As the name suggest, the data of the picture became binary in order to reduce the computational cost.

Segmentation: the outer regions of the image contains almost pure noise, so this areas are discarded

Thinning: The image must be thinned to enable the minutiae extraction algorithm to properly work.

Minutiae extraction: There are several kinds of fingerprint minutiae, however, this algorithm only considerate the ridge end and the bifurcation.

Characteristic vector: the information of the finger print is stored calculating the distance and the angle between the reference minutiae and the others. This vector is first used to train the network and then to make the comparison

So my work consist in adapt and therefore desig a implementation of this algorithm in a Fpga using a DSP tool based on simulink